Server Hardwareluxx přinásí nové informace o procesorové generaci Zen 3, ovšem ne z pohledu desktopových Ryzen, ale serverových EPYC. Ty mají slibovat cca pětinový nárůst výkonu, větší cache a vyšší takty.

Odměníme každého! Vyplňte komunitní průzkum a získejte luxusní ceny

Kdo jste, na čem a co hrajete, jaký obsah konzumujete a jaký vztah máte k AI? Věnujte nám pár minut a jako dárek za vyplnění získáte slevu na nákup a šanci získat také další luxusní ceny.

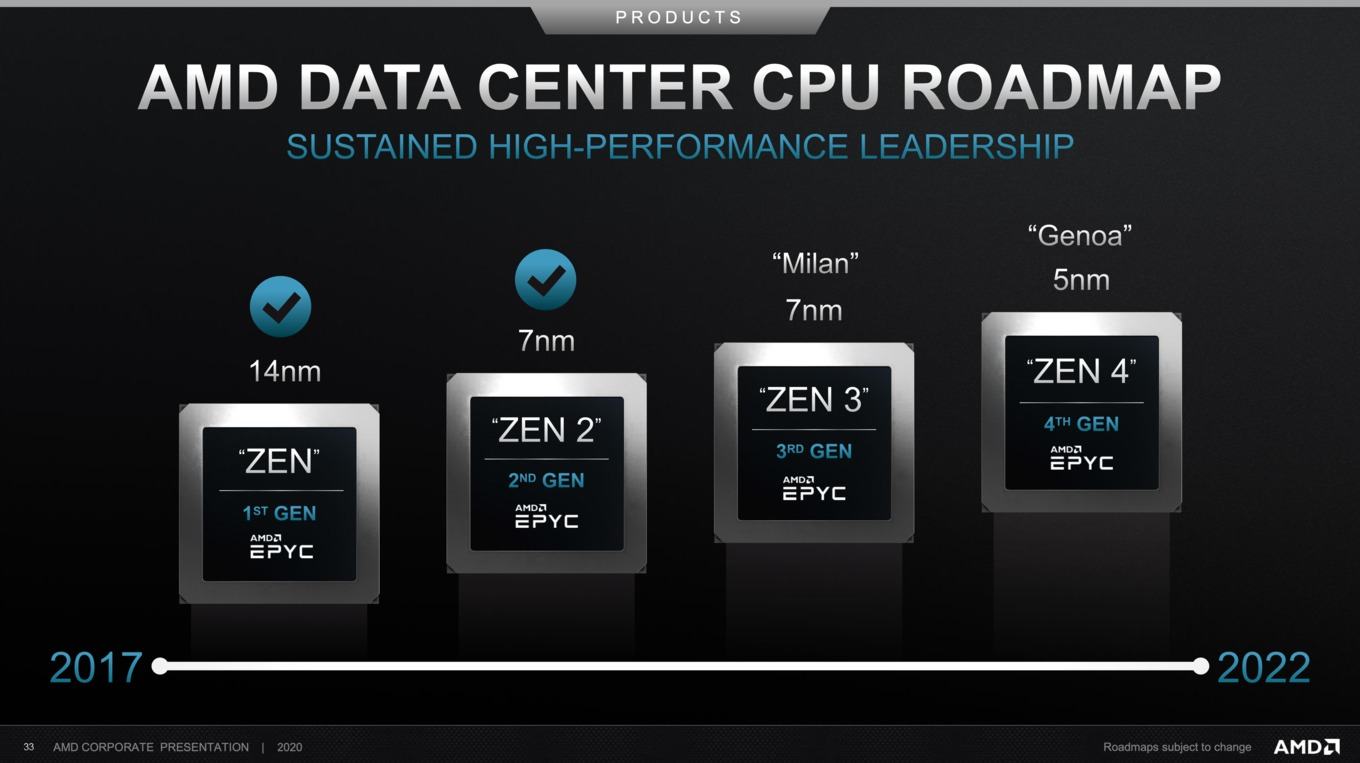

Pětina výkonu navíc nevypadá zase tak špatně, když si uvědomíme, že Zen 3 s největší pravděpodobností nebude o navyšování počtu jader, jichž tak budeme mít stále osm na čiplet a díky EPYC s osmi čiplety jich tak bude maximálně 64. Navýšení výkonu tak bude právě o nové architektuře a také o pracovních taktech. Respektive spíše právě o nové architektuře, která bude zahrnovat i větší cache, jak sděluje server Hardwareluxx. Ten se odkazuje na jistou interní prezentaci firmy AMD.

Z následující tabulky je jasně vidět, že platformy Rome a Milan budou velice podobné, a to podstatné se tak bude odehrávat přímo v samotných čipletech. Je ostatně možné, že AMD využije ty samé, maximálně pak mírně upravené I/O čipy.

| Generace EPYC | Naples | Rome | Milan | Genoa |

| Platforma | SP3 | SP3 |

SP3 | SP5 |

| Konfigurace jader | 32x Zen | 64x Zen 2 | 64x Zen 3 | >64x Zen 4 |

| CCD / L3 Cache | 8 jader na CCD 2x 16 MB L3 Cache |

8 jader na CCD 2x 16 MB L3 Cache |

8 jader na CCD 1x 32 MB L3 Cache |

? |

| Výrobní proces | 14 nm | 7 nm | 7 nm | 5 nm |

| RAM | DDR4 | DDR4 | DDR4 | DDR5 |

| PCIe | PCIe 3.0 | PCIe 4.0 |

PCIe 4.0 | PCIe 5.0 |

| TDP | 120 - 180 W | 120 - 225 W | 120 - 225 W | 120 - 240 W |

Pokud jde o uváděné 20% zvýšení výkonu, pak 15 procentních bodů má jít na vrub právě vyššímu IPC - výkonu na takt - díky vylepšené architektuře. Očekává se především to, že už zmizí čtyřjádrové jednotky CCX s vlastní L3 cache a celý čiplet se bude chovat jako jedna osmijádrová jednotka s celkovou L3. Zbylých 5 procentních bodů by tak šlo na vrub taktům.

Zdroj ale také uvádí, že některé nové modely z generace Milan by mohly oproti svým předchůdcům nabídnout i výrazně vyšší nárůst výkonu, než je 20 % a jiné zase méně. To bude v podstatě záviset na počtu jader s nepřímou úměrou, čili čím víc jader, tím nižší nárůst výkonu.

Co se týče konfigurace cache, nově by tu tak měla být jednotná L3 cache určená pro všechna jádra čipletu, než aby byla rozdělena na dvě poloviny pro čtyři a čtyři jádra. Ovšem celková kapacita zůstane na 32 MB. Navýšení kapacity tak platí pro L2 cache, čili vlastní cache pro každé jednotlivé jádro, která má mít dvojnásobných 1024 kB. Samozřejmě ale bude i nadále možné navýšit kapacitu L3 cache na jádro tím, že se některá jádra v čipletech deaktivují. Pokud tak využijeme třeba všech osm čipletů po čtyřech jádrech, získáme tím 32jádrový EPYC s plnou kapacitou 256 MB L3 cache.

Tomu všemu by tak měla odpovídat i nabídka desktopové generace Vermeer. Ta by si mohla v turbu sáhnout již snad na takt 5 GHz, ale ty hlavní změny budou představovat nové čiplety se Zen 3.