První zprávy o chystaných procesorech AMD Zeppelin se objevily již někdy v polovině minulého roku, kdy se ukázalo, že tyto čipy budou moci pracovat i s výkonným GPU vybaveným paměťmi HBM2. Nyní se informace o Zeppelinu objevily v linuxovém changelogu.

Odměníme každého! Vyplňte komunitní průzkum a získejte luxusní ceny

Kdo jste, na čem a co hrajete, jaký obsah konzumujete a jaký vztah máte k AI? Věnujte nám pár minut a jako dárek za vyplnění získáte slevu na nákup a šanci získat také další luxusní ceny.

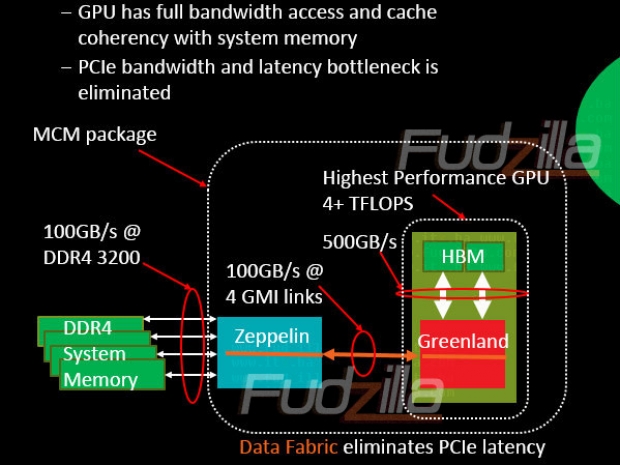

New Citavia Blog zveřejnil nové informace týkající se kódového označení, které se objevilo v minulém roce. Jde o AMD Zeppelin, tedy procesor vybavený až 32 jádry Zen a výkonnou grafikou s HBM2. V minulém roce se mluvilo ještě o grafickém jádru vycházejícím z Greenland, ovšem AMD od té doby změnilo názvosloví, a tak můžeme nyní mluvit o generaci Polaris a GPU Vega 10. Zeppelin ale nebude monolitický čip, ale MCM (Multi Chip Module), na němž bude více čipů propojených pomocí nového rozhraní. Další nové podrobnosti přímo o těchto chystaných procesorech ale nejsou známy.

Nyní se ale objevil nový záznam v linuxovém changelogu podepsaným inženýrem firmy AMD, který přímo zmiňuje procesory Zeppelin:

| AMD Zeppelin (Family 17h, Model 00h) introduces an instructions retired performance counter which indicated by CPUID.8000_0008H:EBX[1]. And dedicated Instructions Retired register (MSR 0xC000_000E9) increments on once for every instruction retired. Signed-off-by: Huang Rui <ray.huang@amd.com> — arch/x86/include/asm/cpufeature.h | 1 + arch/x86/include/asm/msr-index.h | 3 +++ arch/x86/kernel/cpu/perf_event_msr.c | 30 +++++++++++++++++++———– 3 files changed, 23 insertions(+), 11 deletions(-) + core_complex_id = (apicid & ((1 << c->x86_coreid_bits) – 1)) >> 3; + per_cpu(cpu_llc_id, cpu) = (socket_id << 3) | core_complex_id; |

Už v dřívejším slidu z prezentace je zřejmé, že AMD se chystá využít nové rozhraní označované jako GMI (Global Memory Interconnect), jehož čtyři linky dokáží nabídnout celkovou propustnost 100 GB/s a poslouží k propojení jádra Zeppelin s GPU a paměťmi HBM2. To je daleko vyšší propustnost, než jakou nabídne PCI Express a také se má podstatně snížit latence z 500 ns. Není ale jasné, zda označení Zeppelin platí pouze pro soubor jader Zen, nebo pro celý MCM procesor. Ten má využít dnes již běžné paměti DDR4, a to ve čtyřkanálovém zapojení s kapacitou až 256 GB na kanál.

Otázka je, jaký výkon můžeme od celého procesoru očekávat, ovšem starší zprávy mluví o tom, že samotné GPU nabídne i více než 4 TFLOPS. První vzorky by mohly být dány dohromady v singapurské továrně Fab 12 společnosti UMC, kde se kompletují také GPU Fiji. V hi-end variantě by šlo o složitou soustavu dvou 16jádrových procesorů Zen a jednoho GPU Vega 10, do čehož ještě nepočítáme paměti HBM2.

Zdroj: