Detaily o „monstru“ IBM Power5

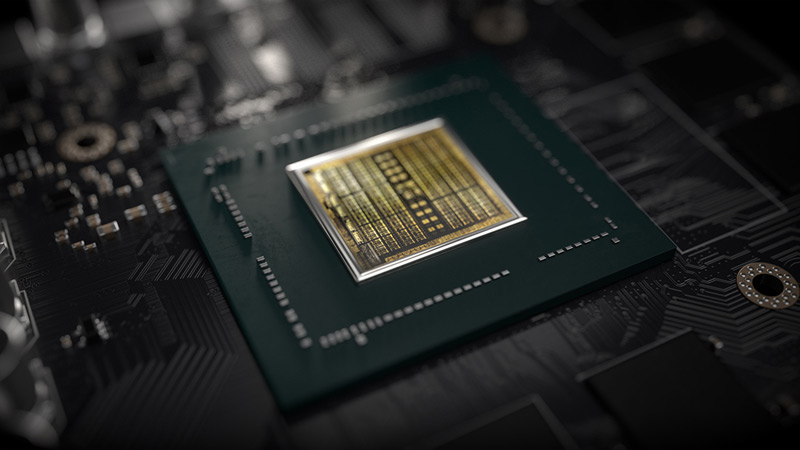

Výroba procesoru spoléhá i tentokrát na 0,13mikronovou technologii s CopperSOI 8-vrstvým procesem. I přes v současnosti nejlepší výrobní proces (nepočítáme-li vzorky 90nm Prescottu) je velikost jádra 389mm2 a počet tranzistorů dosahuje 276 milionů. Pro srovnání – Itanium 2 „Madison“ má plochu čipu 450mm2 a tranzistorů kolem 410 milionů. Ovšem co je u Power5 strhující je počet pinů – 2313 signálových a 3057 napájecích, celkem tedy 5370 „nožiček“.

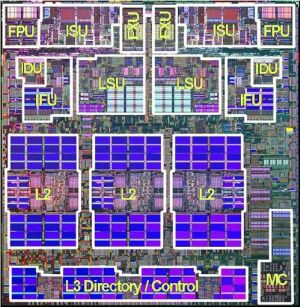

Teď přichází složitá trochu počítání – procesor obsahuje celkem čtyři čipy, z nichž každý se skládá z dvou jader. Každé jádro podporuje navíc multithreading s dvojicí logických CPU a po následném vynásobení tak získáváme 16 logických CPU pro celý Power5. Každé jádro (kterých je tedy na procesoru osm) obsahuje 120 registrů pro celá čísla a FP, 8 jednotek pro zpracování (až 5 instrukcí za cykl a 4 FLOPs za cykl), 64kB instrukční L1 cache (2-way set associative) a 32kB datové L1 cache (4-way set associative). Každá dvě jádra sdílí také 1,92MB L2 cache (10-way set associative), která je rozdělena na tři nezávislé sběrnice po 640kB. Jádra podporují i vylepšený prefetch pro rychlejší práci s pamětí.

Power5 je schopná pracovat až v 64-cestném SMP (simultánní multiprocessing), počítáme-li i multithreading, lze pak tedy propojit až 128 logických CPU v jednom systému. Důležité je, že sběrnice mezi dvěma sousedními čipy na procesoru běží na frekvenci jádra (každým směrem tedy vede 128-bitový link na 2GHz), zatímco dva čipy, které leží na opačné straně „knihy“ (spojení dvou procesorů, viz níže), jsou pak propojeny sběrnicí o poloviční rychlosti. Posíleny byly i přenosy mezi více procesory, mezi procesorem a L3 cache, pamětí apod. Na čipu je nyní integrován i paměťový řadič. Propustnost mezi jádrem a systémovou pamětí by se měla zvýšit oproti Power4+ asi o polovinu, tedy na hodnotu přes 20GB/s.

Každý čip Power5 má na procesoru svoji L3 cache o velikosti 36MB, která pracuje na poloviční frekvenci jádra (oproti třetinové u Power4). Propustnost tak díky 1GHz a 256-bitové sběrnici stoupá až na 32GB/s. Navíc můžeme současně přistupovat k hlavní paměti (přes 20GB/s) a máme tu 4 čipy Power5, takže se nám celková šířka paměťového pásma přehoupla přes 200GB/s!

Nový procesor IBM bude podporovat nejspíše paměti DDR333 nebo DDR400, samozřejmě registrované s podporou ECC. Propustnost b pak byla 21GB/s, resp. 25,6GB/s pro každý čip. Typický 64-cestný server s Power5 by měl podporovat až 1TB paměti.

Na procesoru jako takovém tedy můžeme najít 4 čipy Power5 po dvou jádrech a čtyři čipy po 36MB L3 cache. Dva takové procesory, z nichž každý měří 95x95mm, mohou být spojeny v „knihu“, což je úzké provázání za vzniku 16-cestného SMP systému. Aplikace v hi-endových serverech pak může být následující – máme 4U rack, do kterého se vejdou dvě takové „knihy“, tedy 32 logických CPU. Výkon každého racku pak bude 2 TFLOPs, velikost paměti 2TB a její propustnost 2TB/s. Celkem bude v takovém racku 576MB L3 cache pro procesory. Spojení čtyř „knih“ do jednoho systému pak znamená velice výkonný server, který může následovat p690 „Regatta“ od IBM.

Výkon procesoru se odhaduje přibližně o 60% vyšší než je tomu dnes u Power4 a Power5 by tak měl překonat i Itanium 2 „Madison 9M“ (nehledě na možnost škálovatelnosti systému). Podle všeho dosáhne IBM i vyššího výkonu než Fujitsu SPARC 64 VI, přestože ten bude vyráběn 90nm procesem. Konec konců, rok 2004, kdy se má Power5 objevit na trhu, je ještě daleko.

Zdroj: The Inquirer