Seznam kapitol

V dnešním článku se zaměříme na technologii vrstvení čipů a integrovaných obvodů, na tak zvaný "stacking". Protože se jedná o perspektivní technologii, která se bude více a více používat, podíváme se na ni dnes trochu podrobněji.

Článků o výrobních technologiích na SHW bylo již několik a dnes budeme pokračovat článkem o stackingu čipů a integrovaných obvodů (ICs, integrated circuits) a několika dalších zajímavých technologiích. Začneme trochu oklikou, protože s tématem stackingu souvisí i několik dalších témat. Jak jsme již několikrát na našich stránkách uvedli, například v souvislosti s projektem

, vrstvení čipů bude čím dál více používaná technologie a 3D stacking se již také stává realitou. Nejedná se z principu o novou technologii a v polovodičovém průmyslu se používají techniky vrstvení již poměrně dlouhou dobu. Vždy je ale co zlepšovat a ne jinak je tomu právě u technologie vrstvení čipů.

Vrstvení čipů - Qui bono?

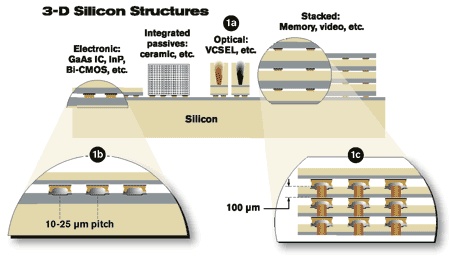

Prvně je možná dobré položit si otázku, proč vlastně čipy vrstvit? Odpověď vás asi napadne vzápětí - u pamětí tak mužeme integrovat požadovanou kapacitu do několika čipů a ty navrstvit na sebe. Více čipů tak dostaneme na menší plochu a v oblasti zapouzdření integrovaných obvodů má tato technologie potenciál s 3D stackingem v budoucnosti přinést menší revoluci. Techniky vrstvení také umožňují spojit různé technologické součásti na úrovni čipu, jako například senzory a nedigitální součásti, a vrstvit jinak různé nekompatiblní výrobní technologie (nebo výrobu rozdělit, například z důvodu úspory - ne všechny části potřebují pro výrobu technologicky nejvyspělejší postupy jako například moderní procesory).

a) 3D struktury mohou integrovat komponenty mnoha typů, b) metody spojení čip-čip, c) spojení waferů/čipů s TSV technologií

Možností, jak navýšit kapacitu pamětí nebo jak integrovat například více tranzistorů a aktivní logiky na mm2 a udělat to zároveň i co nejlevněji, je samozřejmě více. Kapacita postupně roste s integrací a stále se zmenšující výrobní technologií, případně s nasazením dalších technologií jako SOI (Silicon On Insulator) a s řadou dalších technik. Rostoucí integrace ale přináší i své problémy. Kromě již nezbytných inovací na poli použitých materiálů a výrobních postupů (které jsou samozřejmě čím dál dražší a časově náročnejší) roste i cena zařízení pro litografii, nákladnost těchto technik a čím dál náročnějších výrobních postupů obecně.

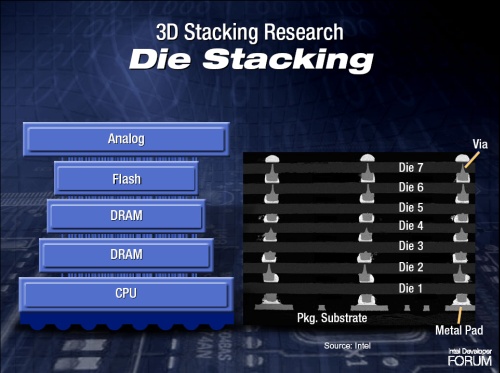

Stacked packaging jako vrstvení čipů na úrovni zapouzdření se již používají zejména u nejvyšších kapacit čipů pamětí, kde standardní postupy nedovolují zatím vyrobit požadovanou kapacitu paměti. Dalším krokem je již 3D integrace, jako například ukázal Intel již na IDF při prezentaci projektu Tera-scale.

Stacking křemíkových vrstev v podání Intelu

Výhody a přínos technologie 3D stackingu

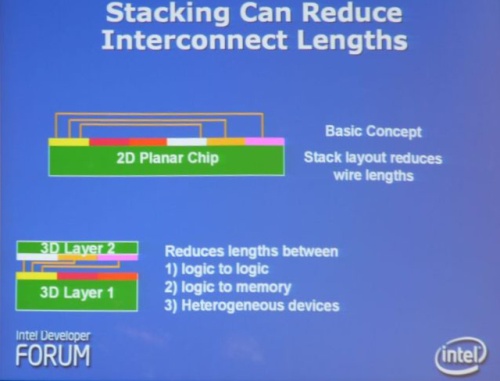

A teď již k samotné technologii vrstvení a 3D stackingu. Jak již zaznělo v předchozí části, 3D vrstvení čipů, které bude obsahovat několik vrstev aktivní logiky, přináší kromě vyšší integrace na mm2 i řadu dalších výhod. Kromě nižší ceny je to také možnost integrace mezispojů a tak zvaných "wire bonds" včetně těch, které jsou jinak například částečně realizovány na úrovni plošných spojů (zejména v případě integrace paměti a procesoru), do samotného (zde je asi dobré podotknout navrstveného) čipu.

Oproti standardnímu "2D" čipu může dojít k výraznému zmenšení vzdálenosti na mezispojích

S rostoucí složitostí obvodu a čipu zde samozřejmě musí být také několik vrstev vodičů. Zde je přínos ve snížení ceny a možném zmenšení výsledného čipu a integrovaného obvodu, což je k ustavičné snaze o miniaturizaci a snížení nákladů velice podstatné. Významné změny jsou také na úrovni mezispojů, kde při dnešním stále vzrůstajícím objemům dat nutně musí růst i propustnosti (jak na úrovni samotného procesoru, tak i mezi jednotlivými čipy nebo procesory ve víceprocesorových systémech). S rostoucí integrací dochází k tomu, že procesory jsou stále rychlejší a stejnou měrou roste i kapacita pamětí, ale šířka paměťové sběrnice a možné propustnosti na této úrovni rostou mnohem pomaleji.

Tento handicap je samozřejmě vůle eliminovat, pokud je to ekonomicky únosné a z hlediska nárustu výkonu a dalších benefitů možné. Částečně například pomocí více kanálů u řadiče paměti nebo s masivní cache (zde jsou možnosti ale značne omezené její možnou velikostí) na úrovni chytře navržené rychlé sběrnice nebo dalšími technikami vzhledem ke konkrétnímu nasazení. Jako jedna z možností zde může pomoci právě technologie 3D vrstvení čipů a integrovaných obvodů. Dále se podíváme na technologii vrstvení a jaké jsou v této oblasti používané metody.