Technologie: Sběrnice PCI Express

- Technologie: Sběrnice PCI Express

- Sběrnice PCI Express

- Vrstvy sběrnice PCI Express

Periferní zařízení počítačů zaznamenávají v posledních letech nebývalý rozvoj. Ten je hnán neustálým tlakem na zvyšování a zkvalitňování toku dat v uživatelských aplikacích. Dnešní aplikace nepožadují pouze vysokou přenosovou rychlost, ale také tzv. quality of service, což znamená, že data musí být v určitý čas přístupná pro zpracovaní. Příkladem může byt typické trhání videa při přehrávání, kdy počítač má dostatek systémových prostředků, ale nemá přístup k právě požadovaným datům. Pro splnění těchto náročných požadavků se v roce 1999 začala formovat skupina firem IBM, HP a Compaq pod vedením firmy Intel. V té době byla vytvořena specifikace "3GIO (Third Generation Input and Output) ARCHITECTURE" tedy třetí generace vstup výstupních zařízení. Dnes je specifikace známa pod obchodním názvem PCI Express. Specifikaci zastřešuje skupina PCI-SIG, tak jako všechny předcházející specifikace PCI a PCI-X.

2. Požadavky na architekturu 3GIO

Uživatelé požadují po moderním elektronickém průmyslu v podstatě dvě protichůdná řešení a to maximalizaci výkonu a minimalizaci ceny. To byl jeden z důvodů tvorby nové specifikace. Dále byla specifikace doplněna o nové požadavky, funkce a vlastnosti:

- Sjednocení přístupu pro více platforem (desktop, mobilní zařízení, servery, pracovní stanice)

- Podpora různých druhů připojení (čip-čip, karta-karta přes konektor nebo kabel)

- Nové mechanické uspořádání

- Zachování současného softwarového modelu

- Detekce a konfigurace PCI Express zařízení pomocí současných mechanismů

- Bootování existujících operačních systémů bez nutnosti modifikovat SW

- Podpora existujících driveru zařízení

- Podpora nových funkcí - vyžaduje úpravu konfiguračního mechanismu

- Výkon

- Nízká režie na vlastní komunikaci a rychlá odezva

- Vysoká přenosová rychlost na pin, z toho plynoucí omezení počtu pinů a nožů konektoru

- Škálovatelná šířka přenosové trasy

- Speciální vlastnosti

- Podpora různých datových typů a pravidel pro přenosy dat

- PowerManagement a úsporné režimy práce

- Identifikovat podporované režimy pro dané zařízení

- Přechod zařízení do daného stavu

- Identifikace současného stavu zařízení

- Generování wakeup sekvencí pro zdroje

- Postupný náběh napájecích napětí

- Podpora QoS (Quality of Service)

- Izochronní datový tok (je požadován nezávislý datový tok v závislosti na čase)

- HotPlug a HotSwap

- Zachování podpory současných zařízení typu HotPlug a HotSwap

- Zavedení ryzího standardu HotPlug a HotSwap bez pomocných signálů

- Jeden softwarový model pro všechny platformy

- Datová integrita

- Podpora detekce chyb na linkové vrstvě jak v datech tak i v paketech

- Oprava chyb

- Podpora současné verze PCI

- Rozšířené generování chyb pro jejich lepší lokalizaci

- Nezávislost na typu přenosového média a napěťových úrovních

- Podpora jednoduchého testovacího mechanizmu

3.1 Architektura PCI - PC do roku 2004

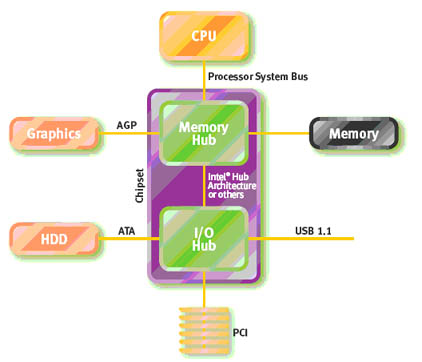

Sběrnice PCI Express se významně odlišuje od svých předchůdců, protože mění celkovou filozofii pohledu na sběrnice, tak, jak je známe do dnešních dnů. Obvyklá představa sběrnice vycházela z propojení několika zařízení sdílející stejnou skupinou vodičů (paralelní nebo sériového). Některé typy sběrnic byly doplněny o vybrané vodiče sloužící pro dekódování daného zařízení, informaci o jeho stavu a synchronizaci hodinovým signálem. Pro lepší představu vyjděme ze sběrnice PCI nebo PCI-X, jak je známe z dnešních počítačů PC (obr. 1).

Obrázek 1: Přehledové schéma současných počítačů do roku 2004 |

Tento typ sběrnice dovoluje paralelní řazení zařízení do slotu nebo přímé propojení mezi zařízeními na desce plošného spoje. Počet zařízení na sběrnici je omezen elektricky dovolenou zátěží sběrnice, logicky může byt sběrnice rozšířena na dalších 256 segmentů oddělených bridgem. Za bridgem může následovat dalších 32 zařízeni. Pracovní frekvence sběrnice PCI je obvykle pevná a to 33 nebo 66 MHz. Sběrnice typu PCI-X řídí pracovní frekvenci hodin podle počtu slotů nebo připojených zařízení.

Tabulka 1 udává přehled jednotlivých typů PCI sběrnic a počet potřebných pinů pro sestavení komunikace mezi zařízeními na sběrnici.

| Typ sběrnice | PCI - 33 | PCI - 66 | PCI-X 66 | PCI-X 133 | PCI-X 266 | PCI-X 533 | ||||||||

| Počet datových bitů | 32 | 64 | 32 | 64 | 32 | 64 | 32 | 64 | 16 | 32 | 64 | 16 | 32 | 64 |

| Počet pinů | 49 | 81 | 49 | 81 | 50 | 82 | 50 | 82 | 36 | 50 | 82 | 36 | 50 | 82 |

| Přenosová rychlost MB/s | 133 | 266 | 266 | 533 | 266 | 533 | 533 | 1066 | 533 | 1066 | 2133 | 1066 | 2133 | 4266 |

| Napájecí napětí | 5/3,3V | 3,3V | 3,3V | 3,3V | 1,5V a 3,3V | 1,5V a 3,3V | ||||||||

Tento přístup klade vysoké nároky na kvalitu signálů, prostor na desce plošného spoje, mechanickou konstrukci konektorů a odolnost proti změnám parametrů sběrnice. Pokud vyjdeme z typického zapojení PCI nebo PCI-X slotu (obr. 2) je nutné zohlednit několik zásad při návrhu zapojení:

- Zatížení sběrnice se musí pohybovat v rozsahu 8-10pf na jedno zařízení, a to podle typu signálu

- Impedance vedení pro klasickou verzi PCI musí byt v rozsahu 60-100Ω a pro PCI-X 57Ω ±10%

- Délka skupin vedení je omezena v rozsahu viz. tab. 2

- Minimalizovat rozdíl délek mezi datovými a strobovacími signály, musí byt menší než 80ps pro sběrnici PCI-X

Obrázek 2: Příklad zapojení PCI zařízení

Dále jsou tyto parametry omezeny elektrickými vlastnostmi materiálů plošných spojů a konektorů, kde se používají obvykle materiály FR4. Pro klasické PCI stačí 4 vrstvy a pro PCI-X je doporučeno vrstev 6. Takovéto omezení není jednoduché dodržet, protože se jedná o vodiče, které mají přesné umístění na nožích konektoru a jsou doplněny o napájecí a další pomocné signály.

Délka signálů | PCI-X | PCI | Jednotka | |||

min. | max. | min. | max. | |||

CLK | vedení | 2,4 | 2,6 | 2,4 | 2,6 | palce |

CLK | zpoždění | 360 | 468 | - | - | ps |

AD[31:0] | vedení | 0.75 | 1.5 | - | 1.5 | palce |

AD[31:0] | zpoždění | 113 | 270 | - | - | ps |

AD[63:32] | vedení | 1.75 | 2.75 | - | 2.0 | palce |

AD[63:32] | zpoždění | 263 | 495 | - | - | ps |

Jako příklad uveďme část plošného spoje sběrnice PCI-X 533 viz obr. 3. Jak je vidět, konstrukce plošného spoje je poměrně komplikovaná a klade vysoké nároky na návrhový systém. Je nutno podotknout, že takto navrženou sběrnici bude možné používat maximálně pro jeden slot. V případě potřeby dalších slotů pracujících na této frekvenci je nutné použít komplikovanější HOST-PCI bridge se dvěma oddělenými sběrnicemi PCI-X. Počet vodičů se zdvojnásobí a systém přechází na architekturu typu peer-to-peer.

Obrázek 3: Část plošného spoje sběrnice PCI-X 533 |

3.1.1 Rekapitulace

Z výše popsaného výčtu jsou zřejmé nevýhody dnešních PCI zařízení a pochopitelný tlak výrobců na změnu koncepce, hlavně v oblasti zvýšení přenosové rychlosti, zkvalitnění datového přenosu, úspory místa na plošných spojích, snížení elektromagnetického vyzařování (EMI), zjednodušení návrhu plošných spojů a sjednocení přístupu ke sběrnicím pro všechna zařízení.

Omezení architektury PCI:

- Velikost přenášeného bloku dat není omezená, díky tomu není možné jednoznačně definovat velikost bufferu, čímž může docházet k častému odpojování zařízení od sběrnice

- PCI zařízení může vkládat velký počet wait-state

- Paměťově orientované operace vyžadují spolupráci s cache procesoru, aby byla zajištěna koherence dat - snížení výkonu CPU a PCI

- Přenos dat je omezen pouze na transakce v délce 32/64 bitů

- Na sběrnici může probíhat pouze jedna transakce a to, jen jedním směrem

- PCI master neví, jestli cílové zařízení může transakci přijmout - retry