Nedávno se objevila zpráva, že Samsung bude nucen odložit nástup svého klíčového 3nm procesu do roku 2022. Klíčový proces je to proto, že se na něm objeví nová generace tranzistorů.

Odměníme každého! Vyplňte komunitní průzkum a získejte luxusní ceny

Kdo jste, na čem a co hrajete, jaký obsah konzumujete a jaký vztah máte k AI? Věnujte nám pár minut a jako dárek za vyplnění získáte slevu na nákup a šanci získat také další luxusní ceny.

Odložení nástupu 3nm procesu by mohlo přijít i bez přispění koronaviru a nám může být vcelku jedno, zda ten k tomu přispěl, nebo ne. Důležité je, že se 3nm proces firmy Samsung už dle jí samotné (via Hardwareluxx) odkládá na rok 2022. Krom potvrzení této skutečnosti tu ale máme i nějaké podrobnosti, dle nichž mají být první vzorky 3nm čipů k dispozici v příštím roce a během roku 2022 už opravdu odstartuje masová produkce.

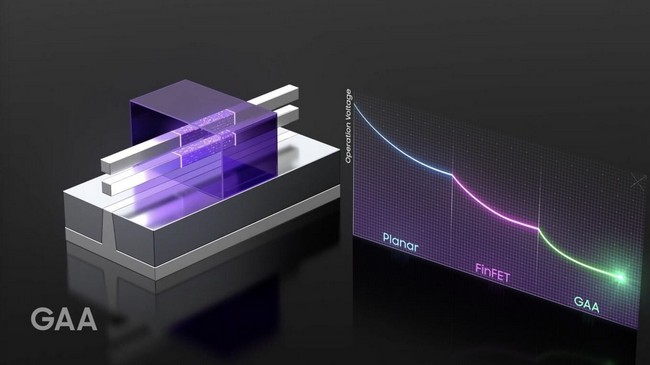

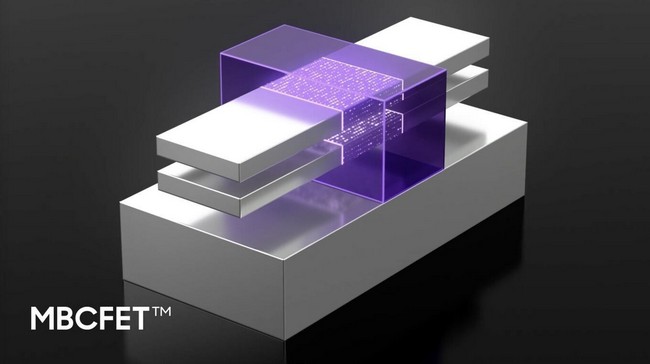

Obecně pak mluvíme o tom, že se zde použijí nové tranzistory typu GAA - Gate All Around, ovšem zpráva mluví specificky o tranzistorech MBC či MBCFET. To se ovšem nevylučuje, neboť MBC jsou jeden z typů založených na GAA, který využije tzv. Nanosheet. Dá se říci, že MBCFET mají být tím pravým a hlavním, co se vyvine v rámci skupiny GAA a ten hlavní rozdíl ukazují dva okolní obrázky. GAA (Nanowire) využívají tenké kanály vedoucí skrz hradlo tranzistoru, zatímco v případě MBC jde o velké a ploché kanály, což znamená i o to větší plochu, kterou zasáhnou do hradel. Takovéto tranzistory bude také možné lépe vyrábět na míru svému účelu, čemuž bude jednoduše odpovídat šířka a počet kanálů.

Potvrzuje se nám také původní předpoklad, že Samsung tranzistory GAAFET přeskočí a rovnou začne vyrábět čipy pomocí MBCFET. Dnes se dozvídáme, že oproti blíže nespecifikovanému 7nm procesu se očekává snížení spotřeby o rovnou polovinu při zvýšení výkonu o 30 procent. Na čipu pak má také jeden takový tranzistor zabrat asi o 45 procent menší prostoru, a to právě i díky novému designu tranzistorů, který v podstatě představuje již klasické FinFET položené na bok. A nenechme se mýlit, opravdu to neznamená možnost vrstvení celých tranzistorů na sebe, jak popisuje server techPowerUp. I když myšlenka je to zajímavá.

Vrstvením tranzistorů by se dalo dosáhnout podobně jako v případě pamětí NAND Flash výrazného zvýšení jejich hustoty na dané ploše, i když zde nejde o paměťové buňky, ale o logické čipy. Je otázka, zda by vůbec bylo vhodné čipy takto zahušťovat a zmenšovat jejich plochu. Výtěžnost z waferu by samozřejmě mohla být vyšší, ale na druhou stranu by se prodloužila doba jejich zpracování a zvětšil prostor pro chyby, nehledě pak na to, že takovéto zmenšení by se nutně odrazilo na kvalitě chlazení, respektive možnostech odvodu tepla z malé plochy.

Proč ale vrstvit tranzistory na sebe, když můžeme skládat vedle sebe jednotlivé čipy? Právě o tom jsou nové a pokročilé metody pro pouzdření a lze očekávat, že v době, kdy bude aktuální i 3nm proces firmy Samsung, tyto metody budou už velice aktuální.

Co se týče konkurentů firmy Samsung, pak Intel dříve udával, že využije první tranzistory typu GAA v roce 2023, ale není jasné, zda to stále ještě platí. Co se týče firmy TSMC, v jejím případě víme jen to, že její 3nm technologie N3 je také na cestě (rok 2021/22) a že se v jejím případě zvažují různé tranzistorové designy.