Seznam kapitol

Nová grafická karta založená na grafickém čipu Fiji se jistě v krátké době stane novou vlajkovou lodí grafických karet od společnosti AMD. Chcete už dnes vědět, jakou asi bude mít Fiji architekturu a výkon? Můžete tedy spekulovat s námi.

Architektura FIJI (spekulace)

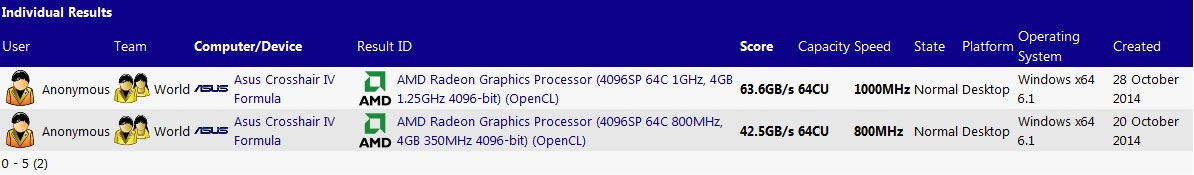

Věřte nebo ne, ale pro (a snad i úspěšné) odhalení architektury grafického čipu Fiji nám postačí pouze pár údajů, jako je celkový počet Stream Procesorů a počet ROP jednotek. Údaj o tom, že Fiji bude obsahovat celkem

4096 SP

, je už nějakou dobu známý a nic nenasvědčuje tomu, že by šlo o nějaký podvrh.

- pro zvětšení klikněte na obrázek -

S počtem ROPs je to ale už horší. Na internetu se nejčastěji pro Fiji uvádí hodnota 128 ROPs jako "zaručená". Bohužel ale žádná taková informace ověřená nikde není, a tak nám nezbývá nic jiného, než začít trochu počítat a spekulovat.

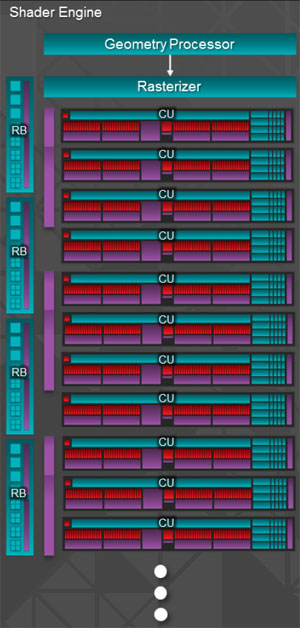

Vraťme se tedy k jednotce nazvané

Shader engine

(SE). Tato SE jednotka vlastně představuje klasickou grafickou pipeline se vším všudy a obsahuje tedy geometry procesor, rasterizér, stream procesory i Rop jednotky. Kdo četl náš článek o grafické pipeline, určitě ví, jak tato pipeline funguje, ale já to pro jistotu raději a velmi stručně zopakuji.

- Imput Assembler složí primitivní geometrický tvar v prostoru (nejčastěji triangl)

- Vertex shader a geometry shader (někdy je využito i teselace) provedou na tomto trianglu nějakou manipulaci s jeho vertexy v prostoru (posunutí, přidání odebrání...)

- Rasterizér vezme tento (v prostoru již finálně umístěný) triangl a pomocí interpolace ho převede do 2D prostoru (vytvoří bezbarvé pixely - fragmenty)

- Pixel shader vypočítá fragmentům barvu (z textur pak za pomoci TMU)

- ROP jednotka provede na těchto pixelech testy jako depth či stencil test a podle výsledku je zapíše do frame bufferu (Render target)

Podle dokumentace GCN je rasterizér schopný vzít jako vstupní hodnotu jeden triangl a na výstupu vytvořit až 16 pixelů (fragmentů) v jednom taktu. O všechny tyto fragmenty se pak musí postarat pixel shader, který jim zjistí barvy a odešle je do ROP. Tam jsou provedeny ony testy hloubky (a další věci) a podle jejich výsledku je pak je pixel zapsán do frame bufferu (nebo také ne).

Každá ROP jednotka umí pracovat s jedním pixelem a tak, aby byl plně pokryt výkon rasterizéru, je třeba mít v SE celkem 16 ROP jednotek (tedy 4 RBE). Samozřejmě, že RBE jednotek by tam mohlo být méně (třeba jako u Tonga), ale my budeme předpokládat, že Fiji bude ultimátní grafický čip a bude chtít využít veškerý výkon rasterizéru. Naše první spekulace tedy bude, že každý jeden Shader Engine (SE) grafického čipu Fiji bude obsahovat 4 RBE (16 ROPs).

Než půjdeme dále, ještě si zapamatujeme, že každá SE jednotka se může postarat a rasterizovat

jeden triangl

a jejím výstupem je maximálně

16 pixelů

. Tyto dvě hodnoty udávají propustnost SE a součet propustností všech SE jednotek pak celkovou propustnost grafického čipu v trianglech a pixelech.

Víme tedy, že Fiji bude obsahovat celkem 4096 SP a spekulujeme, každý SE bude obsahovat 4 RBE (16 ROPs). Nyní je tedy nutné pomocí těchto dvou údajů grafický čip nějak správně dopočítat a poskládat.

Celkový počet CU není těžké vypočítat, protože už z minulé kapitoly víme, že každý CU obsahuje celkem 64 SP. Grafický čip Fiji tedy bude obsahovat 4096 / 64 =

64 CU

. Známe-li počet CU, automaticky také umíme spočítat počet TMU = 64 x 4 =

256 TMU

. První jednoduchou úlohu tedy máme za sebou a víme, že

Fiji bude obsahovat celkem 64 CU a 256 TMU

.

Druhý krok už bude krapátko těžší, protože musíme správně určit, do kolika Shader Enginů (a po kolika CU) Fiji rozdělit. Naší jedinou podmínkou bude, aby všechny SE obsahovaly stejný počet CU. Tuto podmínku lze realizovat pouze následujícími způsoby.

Počet Shader Engines | Počet CU v jednom SE | Počet TMU | Max. počet ROP |

1 | 64 | 256 | 16 |

2 | 32 | 256 | 32 |

4 | 16 | 256 | 64 |

8 | 8 | 256 | 128 |

16 | 4 | 256 | 256 |

32 | 2 | 256 | 512 |

64 | 1 | 256 | 1024 |

První i druhou možnost, tedy že by Fiji obsahoval 1 nebo 2 SE, můžeme okamžitě vyloučit, protože při tak nízkém počtu ROP by Fiji neměla šanci pracovat ve 4K a navíc se dokumentace GCN zmiňuje o maximálním počtu 16 CU v jednom SE (to se ale s příchodem novější mikroarchitektury může samozřejmě změnit). Stejně tak bychom mohli vyloučit i 16, 32 a 64 SE kvůli příliš nízkému počtu CU v SE a nereálně vysokému počtu ROP jednotek. Zbývají nám tedy "pouze" dvě možnosti, jak by mohl být grafický čip Fiji sestaven a jak by mohlo vypadat jeho blokové schéma.

Varianta č.1

Tato varianta vypadá jakoby z oka vypadla grafickému čipu Hawaii, pouze s tím rozdílem, že byl navýšen počet CU jednotek v každém Shader Engine z původních 11 CU na 16 CU. Celkově za celý čip pak z původních 44 na 64 CU jednotek.

TMU se pak automaticky navýšily z původních 176 na 256. ROP jednotky však zůstávají ve stejném počtu, jako tomu bylo u Hawaii. Teoretická propustnost takovéhoto grafického čipu by pak byla 4 trojúhelníky na takt a 64 pixel na takt - tedy naprosto stejná jako u grafického čipu Hawaii.

Varianta č.2

Varianta č. 2 by byla proti čipu Hawaii už ale poněkud jiná káva. Navýšen by byl nejen počet CU a TMU, ale také počet ROP jednotek a rasterizérů, čímž by se propustnost takto navrženého čipu proti Hawaii zdvojnásobila a zvýšila na 8 trojúhelníků a 128 pixelů na takt.

Pokud bychom shrnuli parametry obou variant do jediné tabulky a porovnali se současným grafickým čipem Hawaii (R9 290X), vypadalo by to následovně:

| Parametr | Hawaii | Fiji varianta č. 1 | Fiji varianta č. 2 |

| Počet SP | 2816 | 4096 | 4096 |

| Počet CU | 44 | 64 | 64 |

| Počet TMU | 176 | 256 | 256 |

| Počet ROPs | 64 | 64 | 128 |

| Texel fill rate (1000 MHz) | 176 GT/s | 256 GT/s | 256 GT/s |

| Pixel fill rate (1000 MHz) | 64 GP/s | 64 GP/s | 128 GP/s |

| FP32 výkon (1000 MHz) | 5,6 TFlops | 8,2 TFlops | 8,2 TFlops |

Paměťový subsystém

Informace o tom, že Fiji bude využívat paměti typu

HBM

(High Bandwidth Memory) byla

fakticky potvrzena přímo společností AMD

. Tyto stohované paměti přinášejí nejen vysokou šířku pásma a nízké latence, ale díky své velikosti a umístění na interposeru přinášejí také velkou změnu do návrhu PCB grafické karty. Vadou na kráse použitých pamětí typu HBM1 pak jistě bude poměrně skromná velikost o kapacitě 4 GB. My už ale z našich měření o výhodnosti

proti verzím s 2 GB víme, že menší velikost VRAM nemá na snímkovou frekvenci prakticky žádný dopad, důsledky se však projeví v plynulosti renderovaných snímků. To vše samozřejmě pouze za předpokladu, že hra využívá více paměti, než kolik ji grafická karta nabízí.

Další informace, které se týkají námi "kritizované" velikosti HBM, pocházejí od

Joe Macri

(AMD), který uvedl, že v současnosti je vyšší kapacita VRAM často využívána k dosažení vyšší šířky pásma a s pamětí je tak zbytečně plýtváno. V případě HBM, kdy je šířka pásma dostatečná, by se vše mohlo změnit a nároky na velikost VRAM by se tak mohly snížit. O kolik by se tyto nároky mohly snížit však řečeno nebylo a nám nezbývá než věřit, že AMD a zejména jejich tým přes ovladače se s tím nějak vypořádají.

Použité HBM1 paměti tedy nabízejí šířku pásma 128 GB/s na jeden paměťový modul, což při čtyřech modulech činí 512 GB/s. Je to málo nebo moc? No je to poměrně dost, i když současné GDDR5 paměti zase až tak vzdálené nejsou.

Grafický čip Hawaii na referenčních taktech pamětí 5000 MHz (efektivně) nabízí propustnost 320 GB/s a po přetaktování na efektivních 6000 MHz pak 384 GB/s. V současnosti nejrychlejší grafická karta GeForce Titan X nabízí u svých pamětí propustnost 336 GB/s a po přetaktování na efektivních 7800 MHz pak zase 374 GB/s. HBM paměti první generace tedy nabízejí šířku pásma v rozmezí 33 - 52 % vyšší než to, co dnes mohou poskytnout paměti typu GDDR5.

Na rozdíl od pamětí, které byly avizovány přímo společností AMD, velkou neznámou zůstává velikost použité L2 Cache (L2$). Grafický čip Hawaii využívá při svých 2816 SP L2$ o velikosti 1024 MB a stejnou velikost využívá také "neořezaný" čip Tonga s 2048 SP. Dalo by se tedy předpokládat, že Fiji tuto velikost L2$ zdvojnásobí na 2048 MB. Svou roli zde bude ale jistě hrát právě ono využití paměti typu HBM a také fakt, aby se takto veliká L2$ na grafický čip o velikosti cca 550 mm2 vůbec vešla.

Blokové schéma Titan X

Nabídli jsme vám tedy dvě nejpravděpodobnější varianty, jak by mohla architektura grafického čipu Fiji vypadat. Pro nás se jednoznačně lepší variantou jeví varianta č. 2 a proto se k ní také přikláníme jako ke scénáři více pravděpodobnějšímu. Použití 8 Shader Enginů nabízí proti 4 Shader Enginům dvojnásobný geometrický výkon a stejně tak je zvýšen i teoretický výkon teselace, tedy ten výkon, který AMD potřebuje navýšit asi nejvíce ze všeho. Konečně, jak nejlépe bojovat s Titan X se 6 GPC (

G

raphics

P

rocessing

C

lusters), než za pomoci 8 SE (Shader Engine)?

Z takto koncipovaného grafického čipu by pak mohly vycházet i další a "ořezanější" varianty. Třeba odstraněním jednoho CU z každého SE a jednoho RBE (4 ROPs) bychom se dostali na variantu s 3584 SP a 96 ROPs, která by jistě nebyla žádným "ořezávátkem", ale za přijatelnější cenu by pak nabídla velmi slušný výkon. A když už jsme u toho výkonu, pojďme se nyní podívat na nějaké ty spekulace.