Máme tu třetí generaci procesorů Zen a Ryzen, která je postavena na CCX, čili Core CompleX. Tak AMD označuje čtyřjádrové celky sdílející mezi sebou paměť L3 cache, ovšem dle Marka Papermastera by to mělo být příště jinak.

Odměníme každého! Vyplňte komunitní průzkum a získejte luxusní ceny

Kdo jste, na čem a co hrajete, jaký obsah konzumujete a jaký vztah máte k AI? Věnujte nám pár minut a jako dárek za vyplnění získáte slevu na nákup a šanci získat také další luxusní ceny.

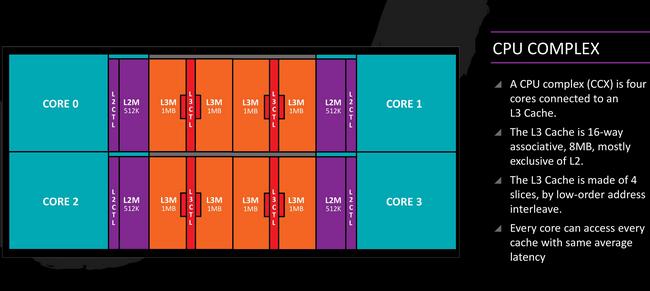

Ať jde o procesory Ryzen první, druhé nebo třetí generace, všechny využívají čtyřjádrové jednotky CCX - Core CompleX. Každé jádro má pochopitelně svou vlastní L1 i L2 cache, ovšem L3 cache je v architektuře Zen sdílena právě čtyřmi jádry jednoho CCX. První dvě generace Zen měly 8 MB na CCX a nyní je to již 16 MB.

Starší procesory založené na čipech Zeppelin s osmi procesorovými jádry tak využívají dva CCX propojené pomocí sběrnice Infinity Fabric. Právě tu musí využít logicky i v případě, kdy se chce jádro jednoho CCX v rámci stejného čipu podívat do L3 cache druhého CCX. To platí i pro moderní 7nm čiplety, jen s tím rozdílem, že ty na rozdíl od Zeppelinů obsahují už jen CPU jádra, L3 cache a rozhraní Infinity Fabric.

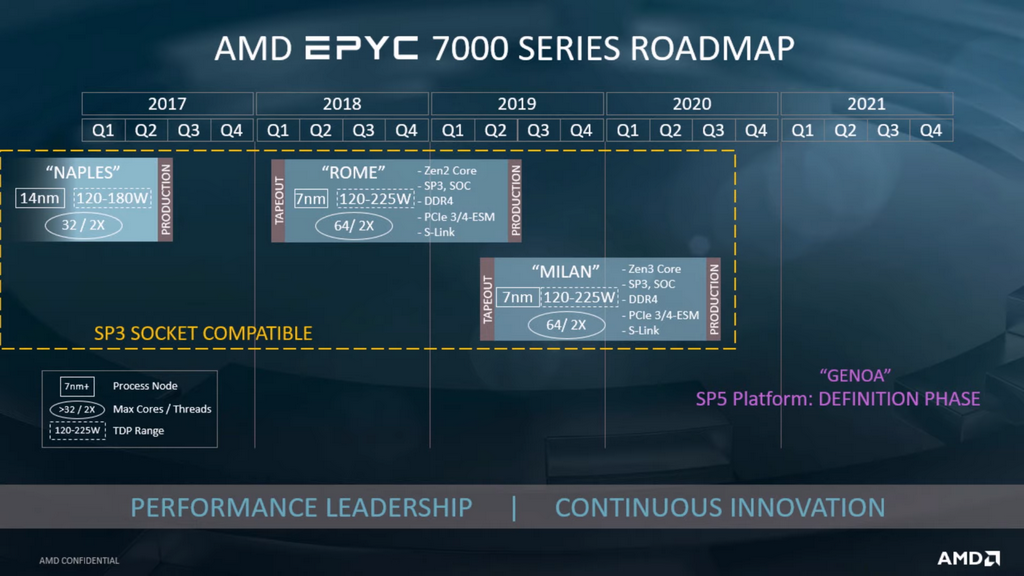

Technická prezentace Marka Papermastera (CTO, AMD), která nyní ze svého původního umístění už zmizela, prozradila, jak by AMD mohlo pokračovat dále v rámci vývoje architektury Zen. Mluvíme tak o Zen 3, kterou už má tedy samotné AMD dávno dokončenou a připravenou pro nasazení, nicméně o detailech se oficiálně ještě nikde nemluvilo.

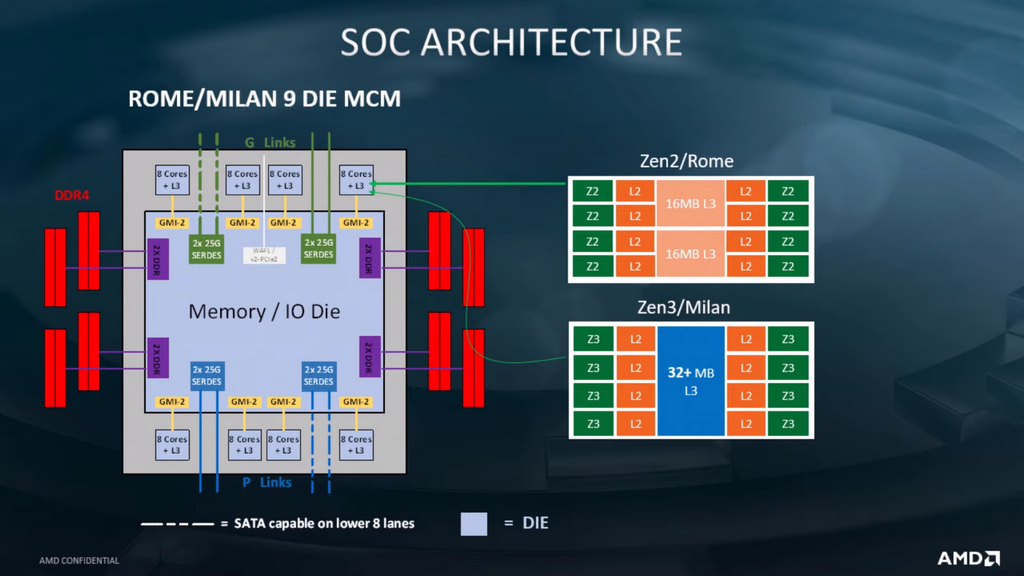

Očekáváme, že v případě procesorů EPYC příští generace založených na Zen 3 budou dnešní Rome nahrazeny procesory Milan. Ty si mají zachovat 64 jader rozdělených mezi celkem 8 čipletů, nicméně jednotlivé tyto čiplety mají obsahovat 32 MB unifikované last-level (čili L3) cache. To by jednoznačně znamenalo konec CCX v dnešní podobě, protože jeden čiplet má dvě samostatné 16MB části L3 cache. Otázka je, co to bude znamenat pro zbytek čipletu a zda AMD "prostě" jen nevytvoří jeden osmijádrový CCX.

A pak je tu ještě jedna neméně zajímavá informace, která mluví o aktualizované implementaci SMT, která má zdvojnásobit počet logických jader na jedno fyzické. To by prostě znamenalo čtyři logická jádra na jedno fyzické a ne dvě jako dnes, přičemž o této možnosti jsme se dozvěděli už dříve. Nyní ale tato infromace pochází opět z jiného zdroje, nicméně to se vůbec nemusí týkat procesorů Milan. Jak ukazuje druhý obrázek z prezentace, tyto procesory mají mít stále stejnou maximální konfiguraci 64C/128T jako Rome, takže čtyřcestné SMT by se mohlo týkat platformy SP5 a procesorů Genoa. Příští EPYC mimochodem můžeme očekávat někdy za rok, čili na podzim 2020.