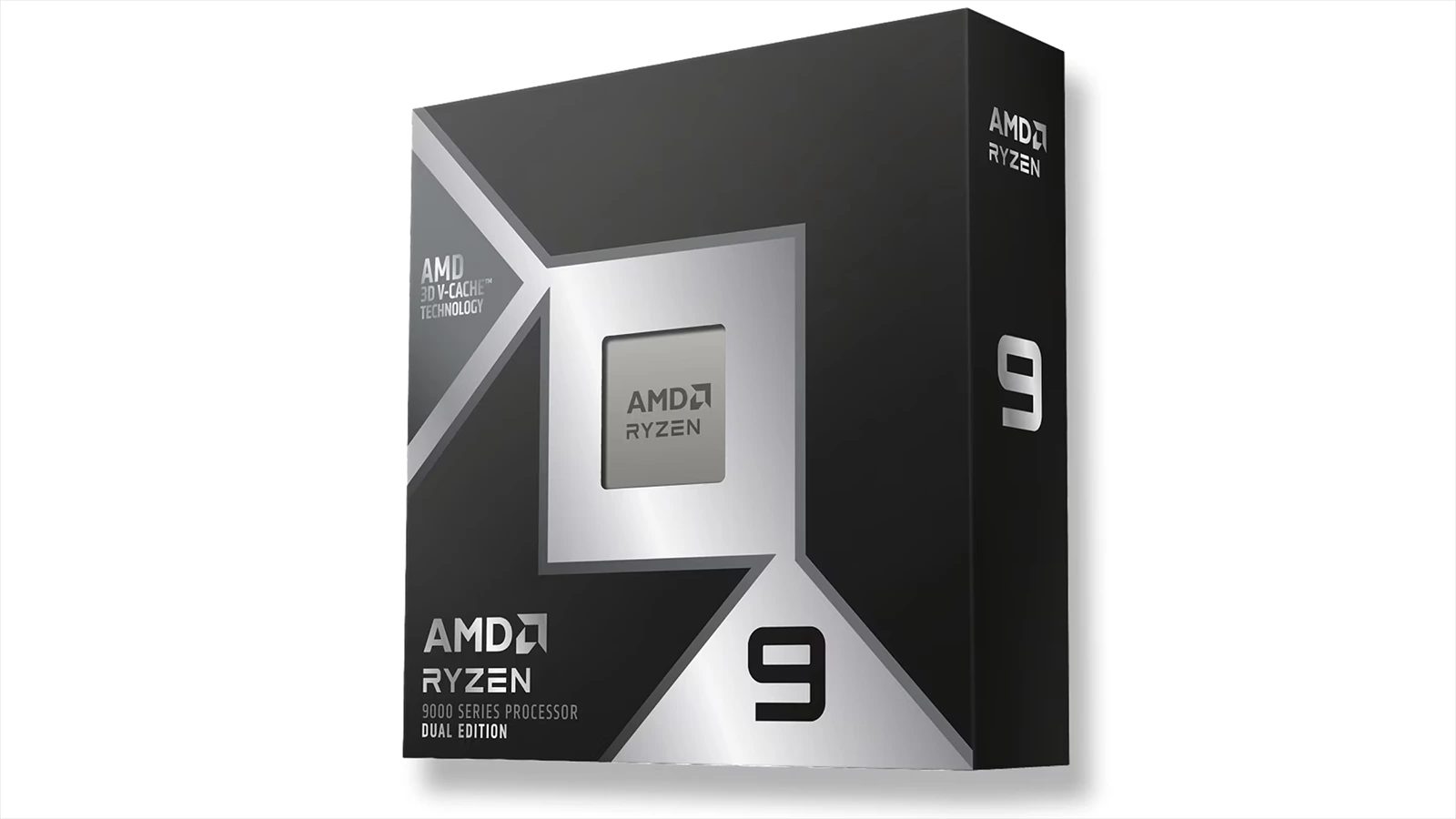

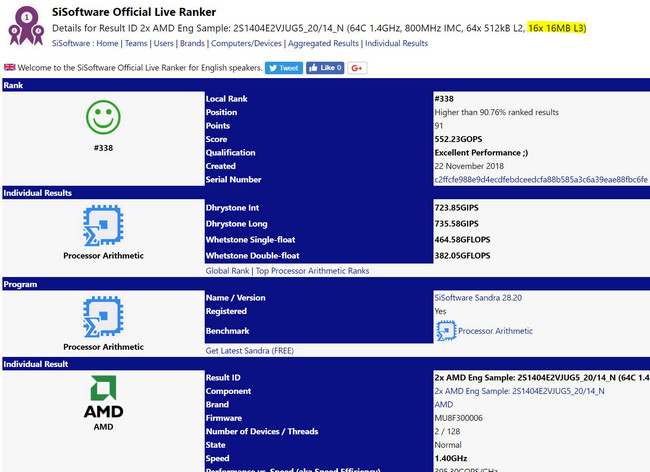

Procesor AMD EPYC tvořený 7nm/14nm procesem a vybavený 64 jádry se už objevil v databázi SiSoft Sandra a hned se ukázala jedna věc. Bude mít celkem 256 MB L3 cache, čili 16 MB na jeden CCX.

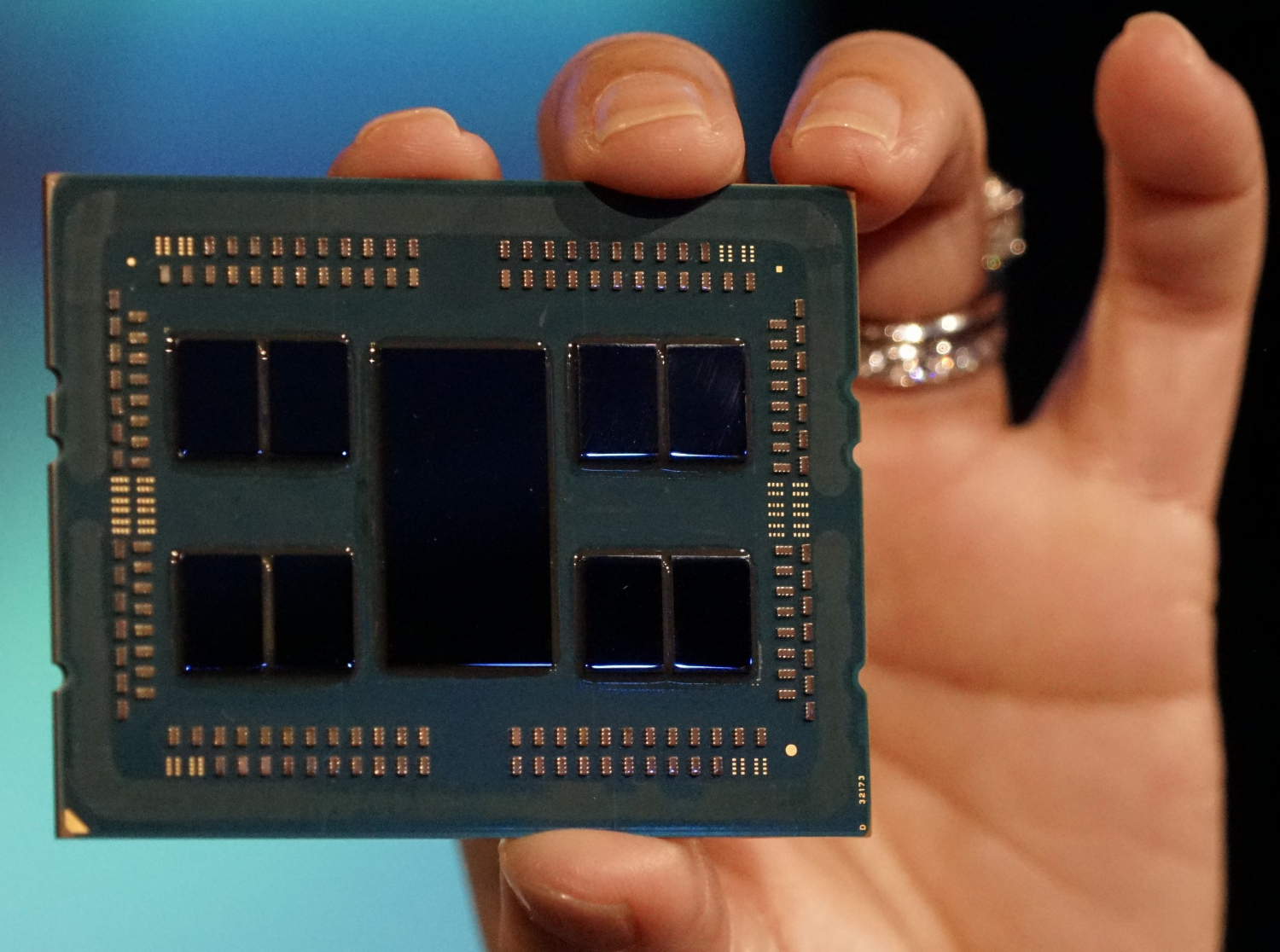

Databáze benchmarků SiSoft SANDRA nám už ukázala leccos nového, jak výrobci testují svůj hardware a nyní jsou to novinky ohledně procesorů EPYC "Rome". Jak už dobře a přímo od AMD víme, půjde o 64jádrové procesory, které se budou skládat ze středového 14nm I/O jádra možná s vlastní L4 cache, ale určitě s linkami rozhraní PCIe a paměťovým kontrolerem (krom jiného) a pak z celkem osmi 7nm "chipletů", osmijádrových kousků procesoru s vlastní L1, L2 a L3 cache. A právě o L3 cache nyní půjde.

V případě dnešních procesorů generací Zen a Zen+ máme jeden osmijádrový čip Zeppelin rozdělen interně na dva čtyřjádrové CCX (Core CompleX), z nichž každý má k dispozici 8 MB L3 cache. Procesory Ryzen 7 tak mají 16 MB L3 cache a EPYC či Threadripper až 64 MB L3 cache.

Sandra však uvádí, že inženýrské vzorky dvou procesorů AMD se 64 jádry, čili bezpochyby zástupci EPYC "Rome", budou mít každý celkem 64x 512 kB L2 cache, což je vzhledem ke každému jádru stejné jako doposud, ale 16x 16 MB L3 cache, čili 16 MB na každý CCX, a to je tedy dvojnásobek oproti generacím Zen a Zen+.

To je celkem pochopitelný dopad využití 7nm výrobního procesu a jeho vysoké tranzistorové hustoty. AMD si mohlo dovolit navýšit kapacitu L3 cache právě i díky rozkouskování celého procesoru na osm chipletů a jedno I/O jádro, přičemž vyšší kapacita paměti by měla napomoci právě ve spolupráci s oním I/O jádrem, které bude pro všechna CPU jádra zajišťovat přístup do paměti a vůbec ke všemu dalšímu v rámci systému.

Spekulovat pak můžeme o kapacitě L4 cache v I/O jádru, která by tam logicky měla být, ale AMD o ní dosud nemluvilo. Pár dní se ale o nové generaci EPYC pozoruhodně přesně vyjádřil The Retired Engineer, který má ve svých materiálech zaneseno 512 MB L4 cache v podobě paměti eDRAM (tu využívá také Intel jako videopaměť pro procesory s grafikou Iris Pro). Ovšem dané materiály nesou také zmínku, že L4 cache bude možná někdy příště, snad v době, kdy už i I/O jádro bude 7nm a ne 14nm?