Architecture Day je už minulost a nyní zbývá odhalit to, co nám přinesla. Už jsme se věnovali 10nm architektuře Sunny Cove, ale zmíněný Foveros jde ještě mnohem dále a chce od základu změnit způsob, jakým se staví výkonné čipy.

My jsme spekulovali o tom, že Intel bude chtít už pořádně využít svou technologii EMIB, ale vypadá to, že ten chce jít i mnohem, mnohem dál. Dá se říci, že spíše než s EMIB má 3D čipová architektura Foveros leccos společného s konceptem tzv. aktivních interposerů. Rozdíl je obrovský. Zatímco EMIB jsou pouhé křemíkové datové spoje, pod okraji čipů, aktivní interposery jsou obvody obsahující síťovou logiku, která slouží k co možná nejefektivnějšímu propojení jednotlivých částí.

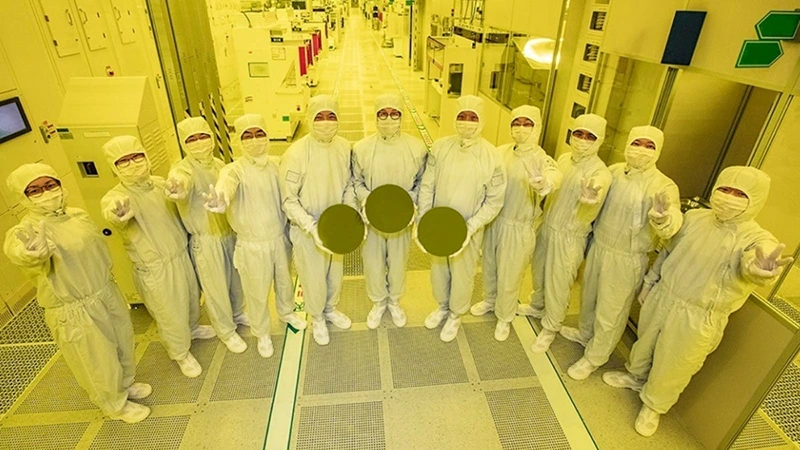

Půjde spíše rovnou o vrstvení počítačových čipů, což není jednoduchý úkol už jen kvůli odvodu tepla z nižších vrstev nehledě na problémy se samotným propojením. Však to dobře poznalo samotné AMD, které mělo velké potíže s výtěžností hotových GPU Vega spojených s paměťmi HBM2.

- klikněte pro zvětšení -

Intel už na Architecture Day prezentoval čip, který s pomocí architektury Foveros integroval do sebe CPU Core i Atom. To by šlo považovat pouze za ukázku, která sama o sobě nemá valný význam, ale dle Intelu byl daný čip vyroben na přání jednoho jeho zákazníka. Podívejme se raději na koncept s tím, že Foveros neznamená, že Intel chce EMIB přeskočit a zapomenout na něj. Využít chce obojí.

Obrázek nahoře ukazuje jednak klasický monolitický design, který dobře známe. Pak to je 2D integrace čipů, čili právě s použitím EMIB, kde jsou vedle sebe samostatně vyrobené čipy propojené pomocí křemíkových můstků pod jejich okraji. Intel zde stejně jako AMD mluví o chipletech a také umožní využití třeba 22nm, 14nm i 10nm technologie najednou. Pak už je to 3D integrace kombinující všechny výhody EMIB s tím, že tu budou vrstvené chiplety. Ty základní budou propojeny křemíkovými můstky a pak samy stejně jako dnešní interposery poslouží k propojení dalších chipletů nahoře. Ovšem nebudou to jen pasivní datové spoje v křemíku, ale logické obvody samy o sobě, čili aktivní interposery. Ale pojďme na to z boku.

Intel sám v dalším obrázku používá termín aktivní interposer, takže už konečně opravdu víme, na čem jsme. Pak je celkem i jasné, jak chce Intel vyřešit problém s akumulací tepla v nižších vrstvách. Dá se totiž uvažovat o tom, že takový aktivní interposer nebude zrovna výkonný čip, který by tvořil velké množství tepla, a proto by s tím ani neměl být problém.

Jak ukazuje boční náčrt, máme tu zcela vespod package, čili procesorovou destičku, pak je to samotný interposer a na něm pak sedí jednotlivé čipy. To vše je propojeno pájenými spoji.

Další snímek však ukazuje první hybridní architekturu x86, která kombinuje právě procesory Core a Atom, oba vyrobené pomocí 10nm technologie. Vespod přitom není pouze prostý interposer, ale procesorové části až na samotná jádra, která jsou nahoře. Už se výslovně nedozvíme, co přesně je POP Memory, nicméně POP obvykle znamená Package on Package, takže z tohoto pohledu jde o samostatné pouzdro s paměťmi, které sedí na pouzdru s procesory. Zde také můžeme zmínit podobu s architekturou ARM big.LITTLE, která také kombinuje méně a více výkonná jádra využívaná pro různě náročné úlohy, což může mít výrazný dopad na spotřebu a výdrž na baterie.

Další dostupný náčrt však opět počítá s tím, že vespod budou energeticky méně potřebné obvody, však B má popisek Low Power Logic a C zase Power Regulator.

Z toho všeho se dá očekávat, že Intel půjde cestou EMIB a Foveros, čili skládaných čipů, které mohou být dále vrstveny. Prozatím se chystá zmíněný hybrid s Core a Atomem, který se dostane na trh v příštím roce.