Není to sice to samé co Chuck Norris Cache, ale i Rambo Cache zní celkem schopně. Vedle ní nám HPC grafiky Xe známé již jako Ponte Vecchio slibují tisíce jednotek EU (dnes jich jsou sotva desítky) a paměti HBM.

Nedávno jsme se dozvěděli o kódovém označení pro 7nm HPC grafiky Xe, a sice Ponte Vecchio a nyní se dozvídáme už daleko zajímavější podrobnosti o tom, jaká bude jejich architektura a jaké technologie bude využívat. Jak se dalo očekávat, základem budou jednotky známé již dnes jako EU, Execution Units. Jejich počet se ale bude moci pohybovat i v řádu tisíců, což by jednoznačně mělo znamenat, že půjde o spojení více čipů. Do toho tu pak máme termíny jako XEMF Scalable Memory Fabric, Rambo Cache, Foveros, HBM, atd.

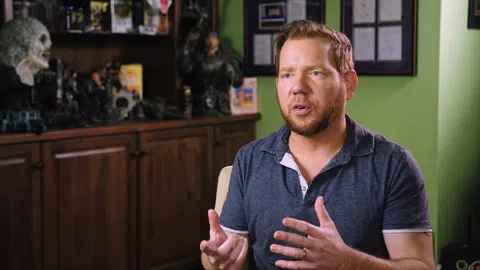

Tyto novinky prezentoval pochopitelně Raja Koduri, který se ale nevěnoval jen HPC řešením. Pro začátek rozdělil chystané Xe GPU na tři proudy, a to:

- Xe LP: integrovaná a low-end GPU

- Xe HP: střední třída, hi-end, datacentra, AI

- Xe HPC: HPC exascale (superpočítače)

První skupina bude zahrnovat typicky 5 až 20W řešení s možností jít až na 50 W. Xe HP pak budou mít 75 až 250 W, což je tedy i desktopová třída a Xe HPC budou prostě a jednoduše papat víc. Nejde přitom jen o rozdělení dle výkonu a spotřeby, půjde i o odlišné mikroarchitektury, což je zřejmé, neboť low-end řešení nebudou potřebovat třeba rozhraní pro propojení více čipů, atp.

Ponte Vecchio tak počítají se 7nm procesem, novým způsobem pouzdření Foveros (plus EMIB) a rozhraním Xe Link založeným na CXL, obdobě Infinity Fabric a podobných. Technologie Foveros přitom spočívá v zapojení různých čipů v rámci jednoho pouzdra, a to jak vedle sebe, tak i nad sebou. Dosud jsme ale měli Foveros spojenou jen s nízkospotřebovými čipy, a to z jednoho prostého důvodu: není jednoduché chladit výkonné čipy v případě, že jsou navrstveny na sebe, takže bude velice zajímavé sledovat, jak to Intel v případě výkonných HPC GPU provede.

Raja Koduri dále zmínil značně vylepšené jednotky EU, které nabídnou 40x vyšší výkon v FP64. Pro jejich napojení na paměťové kanály bude využito nové škálovatelné rozhraní XEMF (Xe Memory Fabric) a co se týče Rambo Cache, půjde o vysokokapacitní cache, která poslouží několika GPU najednou. Právě i díky ní budou moci Xe nabídnout tak vysoký výkon v FP64 a její data budou přístupná i pro CPU. Rambo Cache bude tak přímo sdílena několika GPU Xe napojenými na stejný interposer, pomocí EMIB budou napojeny paměti typu HBM, a tak by se dalo usuzovat, že daná cache bude právě v "patře" jako další vrstva napojená vertikálně díky Foveros. V tomto ohledu jsou ale dostupné informace vágní, jen se ještě dozvíme, že Ponte Vecchio využije až 16 Xe čipletů najednou, takže to bude opravdu pořádný slepenec.

Koduri prozradil nakonec i to, že 7nm technologie Intelu slibuje dvojnásobnou hustotu tranzistorů oproti dnešní 10nm technologii, a tak doufejme, že tentokrát se to Intelu už opravdu podaří.

Vypadá to tak, že Intel to myslí se vstupem do světa samostatných grafických čipů opravdu vážně a že AMD s NVIDIÍ by mohly získat silného soupeře. Ještě před 7nm Xe ale dorazí v příštím roce úvodní 10nm generace, která zatím asi bude zahrnovat jen monolity a tu máme spojenu především s herními produkty a integrovanými grafikami, čili dle nového označení půjde o Xe LP a Xe HP.